SUZAKUを使ってISE WebPackの動作確認をします。

作成する回路は単色LEDを点灯させるだけの簡単な回路です。

(suzaku_starter_kit_guide_fpga_ja参照)

ガイドではVHDLを使っているのですが、ここではVerilogで記述します。

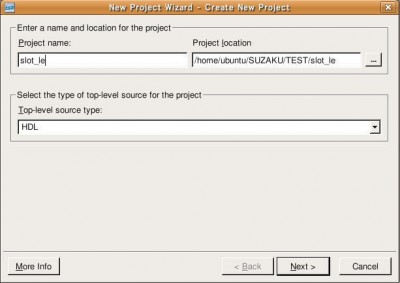

まず、ホームディレクトリに作成したSUZAKUディレクトリにTESTディレクトリを作成します。このTESTディレクトリにプロジェクトを作成します。

端末より”ise”を入力してProject Navigatorを起動します。

起動したら上部メニューより”File”をクリックして”New Project…”を選択します。

開いたウィザードのProject locationに先ほど作成したTESTディレクトリを指定し、Project nameにslot_leを入力します。

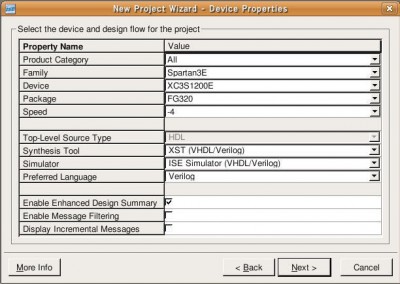

デバイス情報を入力し、Preferred LanguageにVerilogを指定します。

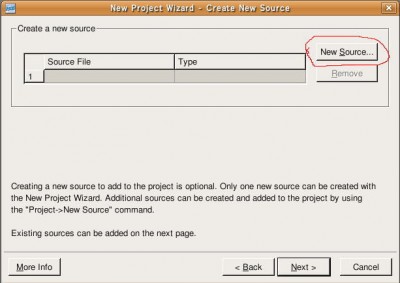

New Sourceをクリックします。

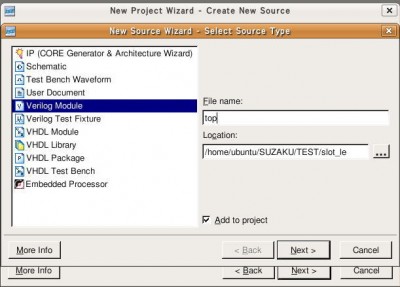

Verlog Moduleを選択し、File nameをtopにします。

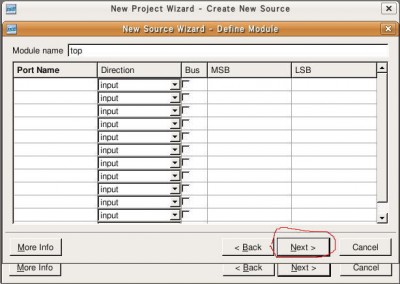

そのままNextをクリックします。

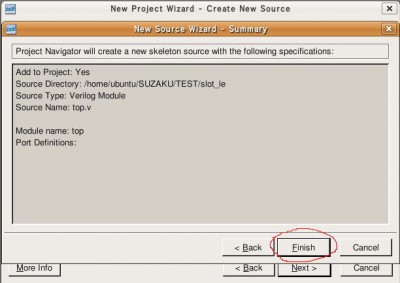

Finishをクリックします。

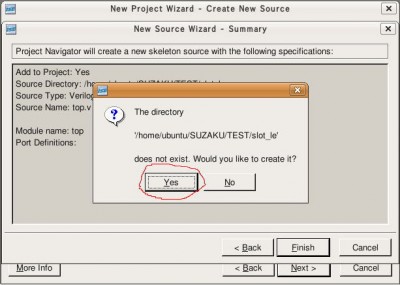

slot_leのディレクトリを作成するか聞かれるので、Yesをクリックします。

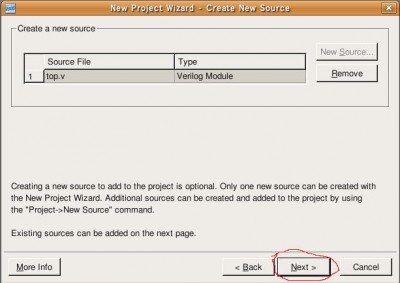

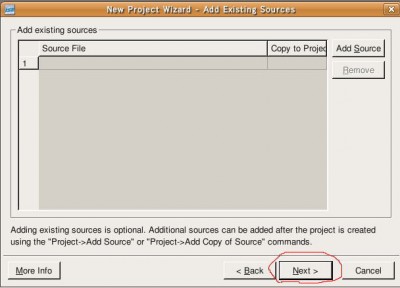

Nextをクリックします。

既存のモジュールを使うときにはここで追加します。

今回は使わないのでそのままNextをクリック。

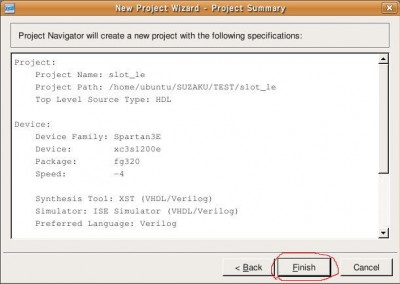

Finishをクリックしてウィザード終了です。

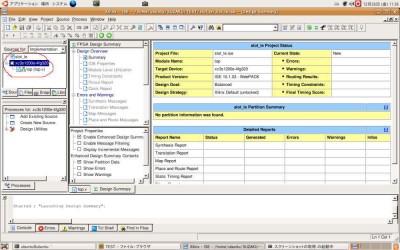

新規プロジェクトslot_leが出来上がります。

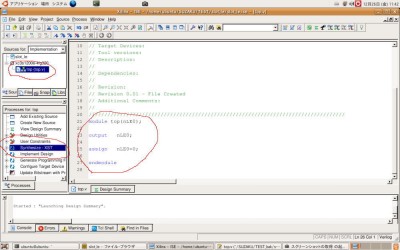

top(top.v)をダブルクリックして開きます。

テンプレートが作成されているので、その中に単色LEDを点灯させるソースコードを作成します。

module top(nLE0);

output nLE0;

assign nLE0=0;

endmodule

作成し終わったら保存し、Synthesize-XSTをダブルクリックして文法チェックをおこないます。

エラーが無くなったら、PACEを立ち上げてピンアサインをおこないます。

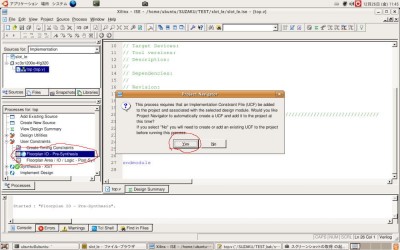

User Constrainsを開き、Floorplan IO-Pre-Synthesisをダブルクリックします。

UCFをプロジェクトに加えるか聞かれるのでYesをクリックします。

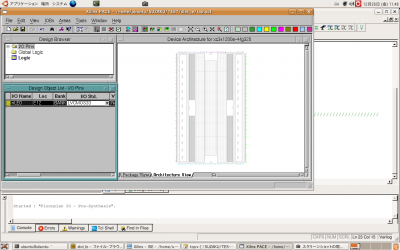

PACEが開いたら、LocにE12を入力し、I/O StdをLVCMOS33に設定します。

ピンアサインが終わったらインプリメントを開始します。

Implement Designをダブルクリックします。

インプリメントが終わったら、FPGAに書き込むbitファイルを生成します。

Generate Programming Fileをダブルクリックします。

エラーがなければ、top.bitが生成されます。

top.bitができたら、JTAGでコンフィギュレーションをおこないます。

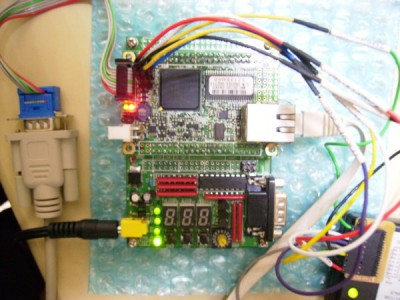

SUZAKUのCON7にダウンロードケーブルを接続し、JP2をショートさせて電源を入れます。

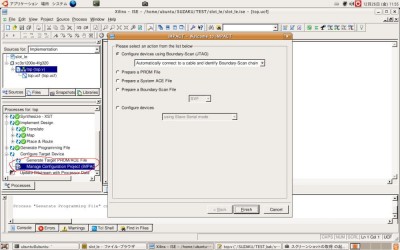

Manage Configuration Project (iMPACT)をダブルクリックします。

Configure devices using Boudary-Scan(JTAG)にチェックが入っているのを確認してFinishをクリック。

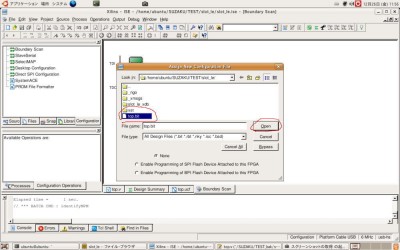

top.bitを選択してOpenをクリック。

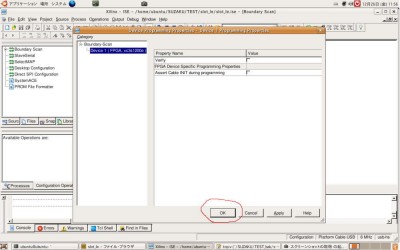

OKをクリック。

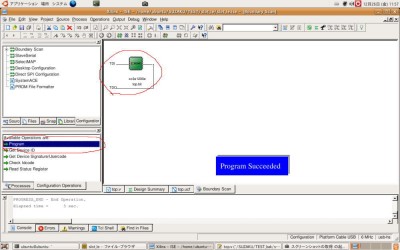

デバイスを選択してProgramをダブルクリックするとダウンロードがはじまります。

単色LEDが点灯しました。