Versys EDAには、SystemCシミュレータがインストールされています。

バージョンは、systemc-2.2.0です。

SystemCは、RTL設計よりも抽象度の高いTLM(Trannsaction Level Modeling)での設計ができます。

ホームディレクトリのVersysフォルダ内に、インバータ(inverter)、リセット付きDFF(dffr)、カウンタ(counter)回路の例題と、TLM2.0が入っています。

まずcounter回路の動作確認をしてみます。

例題のcounter回路があるディレクトリに移動します。

ホームディレクトリより、

$cd Versys/Examples/Versys_Examples/SystemC/counter

移動したら、

$ls

ディレクトリ内に、

・Makefile

・counter.cpp

・counter.h

・test.cpp

があるのを確認します。

$make run

実行され、vcdファイルcounter.vcdが作成されます。

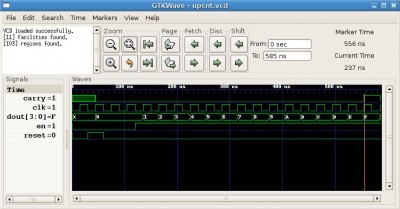

$gtkwave counter.vcd

GTKWaveで波形を確認します。

$make clean

で、vcdファイルが削除され初期状態に戻ります。