Versys EDAには、Verilog to SystemCトタンスレータのVerilatorがインストールされています。

Verilatorは、SystemCテストベンチを用いて、Verilogモジュールの高速なシミュレーションができます。

Verilogシミュレータと同様に、ホームディレクトリのVersysフォルダ内に例題があります。

counter回路の動作確認をしてみます。

例題のcounter回路があるディレクトリに移動します。

ホームディレクトリより、

$cd Versys/Examples/Versys_Examples/Verilator/counter

移動したら、

$ls

ディレクトリ内に、

・Makefile

・counter.v

・test.cpp

があるのを確認します。

$make run

実行され作成されたobj_dir内にvcdファイルcounter.vcdが作成されます。

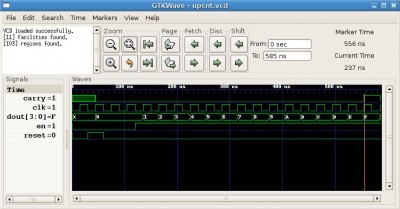

$gtkwave obj_dir/counter.vcd

GTKWaveが開きます。

$make clean

で、obj_dirが削除され、初期の状態に戻ります。

Makefileを使わない場合、以下の手順となります。

$verilator –sc counter.v –exe test.cpp

オブジェクトディレクトリobj_dirができるのでここに移動します。

$cd obj_dir

移動したら、

$make -f Vcounter.mk

オブジェクトファイルができるので、

$g++ -L$SYSTEMC/lib-linux *.o -o Vcounter -lsystemc

実行ファイルVcounterができるので、

$./Vcounter

vcdファイルcounter.vcdが作成されます。