Versys EDAには、VerilogシミュレータのIcarus Verilogと、GPL Cverがインストールされています。

ホームディレクトリのVersysフォルダ内に例題として、インバータ(inverter)、リセット付きDFF(dffr)、カウンタ(counter)回路が、入っています。

counter回路の動作確認をしてみます。

例題のcounter回路があるディレクトリに移動します。

ホームディレクトリより、

$cd Versys/Examples/Versys_Examples/Verilog/counter

移動したら、

$ls

で、カウンタモジュール

・counter.v

と、テストベンチの

・test.v

があるのを確認します。

まずIcarus Verilogを使ってシミュレーションします。

$iverilog -o counter -s test counter.v test.v

-o counterで、出力ファイルcounterを指定します。

この指定をおこなわなかった場合、出力ファイルはaoutとなります。

-s testで、テストモジュール名testを指定します。

この指定は推奨されているようですが、指定しなくても動作するようです。

出力ファイルcounterができているのが確認できたら、

$vvp counter

vcdファイルcounter.vcdができているのが確認できたら、

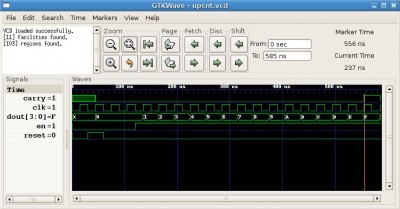

$gtkwave counter.vcd

GTKWavwが開きます。

ツールメニューのSearchをクリックしてプルダウンメニューからSignal Search Treeを選択。

観測したい信号を選択してAppendをクリックすると波形が表示されます。

次に、GPL Cverを使ってシミュレーションします。

Icarus Verilogでシミュレーションしたときにできた出力ファイルcounterと、vcdファイルcounter.vcdを削除します。

$rm counter counter.vcd

シミュレーションをおこないます。

$cver counter.v test.v

vcdファイルcounter.vcdができているのが確認できたら、GTKWavwで波形を表示します。